LVDS (Low-Voltage Differential Signalling)

Low-Voltage Differential Signalling (LVDS) is a standard which specifies the low-level electrical characteristics of a serial communications protocol.

The standard only defines the low-level electrical characteristics, which leaves designers free to specify the data link later, which includes things such as encoding.

Characteristics

| Drive Type | Differential |

| Num. Wires | 2 (excl. GND) |

| Duplex | Half |

| Connection Topology | Point-to-point (LVDS) or multidrop (MLVDS) |

Implementing LVDS On A FPGA

Many of the I/O present on an FPGA can support the differential LVDS protocol. They have built in drivers and receivers that can convert the LVDS signal to and from a stream of 1’s and 0’s.

A serializer/deserializer (SERDES) can be used to convert the stream of bits into bytes of data. This can then be passed into a FIFO for storage, before being handled by processor or other part of the FPGA system.

Mulitpoint LVDS (MLVDS)

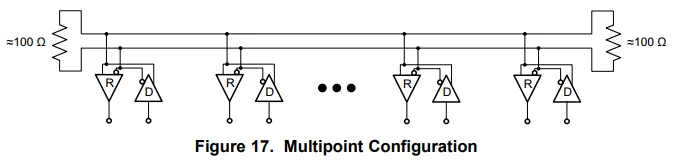

The original LVDS standard was concerned only with point-to-point communications. NSC invented a standard called Bus LVDS (BLVDS) which is a variant on LVDS which allows for a topology of one transmitter connected to multiple receivers.

Multipoint LVDS is now covered by the TIA/EIA-899 standard.

There are two types of receivers for MLVDS buses. Type 1 receivers are compatible with LVDS and use a +/- 50mV threshold. Type 2 receivers allow for Wired-OR type signalling (arbitration), but are not compatible with standard LVDS buses. Some MLVDS transceivers support both types of receivers (for example, the SN65MLVD206B).

TIA/EIA-899 recommends using reflected-wave switching for wired-OR signalling.

RoboNet, a communication protocol used by the Robotic Operating System (ROS) is a data-link layer protocol that uses MLVDS.