QFN Component Package

| Date Published: | |

| Last Modified: |

Overview

QFN is a family of SMD component packages with typically 12-108 leads. The QFN package is commonly used today for higher lead count ICs such as microcontrollers. It is a near chip-scale package, with all the pins being around the perimeter and an optional thermal pad(s) in the center. It is one of the highest pin-density SMD packages without resorting to BGA. Note that there are different pitch footprints within the QFN family! And QFN packages do not have to be square (square is the most common), some rectangular versions exist with a different number of leads on the two sides (they always have the same number of pins on the opposite side).

ERROR: fig-qfn-16-with-ep-3d-model REF NOT FOUND shows a typical QFN package with an equal number of leads on all sides and an exposed pad.

![A 3D render of a typical QFN-16 package with an exposed pad on the bottom center[^digikey-renesas-isl84467irtz-t-ic-switch].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/qfn-16-with-ep-3d-model.png)

A 3D render of a typical QFN-16 package with an exposed pad on the bottom center1.

QFN packages offer benefits over other packages for high-speed circuits, as well as high heat dissipation capabilities. QFN packages are lacking gull-wing leads (like that present on the QFP package), which create noise in high-speed applications. However because the package is sitting right on the surface of the PCB (or very close to it), they suffer more from mechanical/thermal stress than other SMD packages with larger stand-offs, such as the QFP package.

Texas Instruments recommends rounded pads on the QFN package to prevent solder bridging. Also, stencil windows are recommended for the solder paste on the thermal pad so that a limited amount of solder is added. Too much solder can cause the QFN package to “float” around during the soldering process.

A QFN-like package with pins on only two of the fours sides is a SON package (DFN).

Confusingly, NXP names it’s range of QFN packages with SOT… (e.g, SOT-662-1), a name which is commonly reserved for transitory packages such as the popular SOT-23.

Synonyms

2077-02: Freescale’s package code for a QFN-16, 5x3, 3x3mm body package.CP-32-2: Analog Devices package code for a QFN-32, 8x8mm, 0.50mm pitch, 5x5mm body package.HVQFN: NXP’s name for a QFN with wettable flanks.LFCSP: Analog Devices.MLF: Micro-leadframe.MLP: Fairchild Semiconductor2.QFN-UT: Samtech’s name for ultra-thin QFN packages by Samtech.RSB: Texas Instrument’s drawing code for a QFN-40 package.RSN: Texas Instrument’s drawing code for a QFN-32, 8x8 pins, 4.15x4.15x0.80mm body, 0.40mm pitch package3.RQZ: Texas Instrument’s drawing code for a QFN-48, 7x7mm, 0.50mm pitch package.SOT....: NXP’s name for it’s QFN range of packages, not this does not include packages such as the SOT-23, which are NOT QFN packages.T3B: Microchip’s code for a VQFN-48, 7x7x0.9mm, 0.5mm pitch, 5.15x5.15mm EP package4.TMB: Microchip’s code for a VQFN-64, 9x9x0.9mm, 0.5mm pitch, 4.70x4.70mm EP package4.UFD: Linear Technology’s (now Analog Devices) code for a QFN-28, 5x4mm, 0.5mm pitch, 3.65x2.65mm EP5.ZLG: Atmel’s code for a VQFN-48, 7x7x0.9mm, 0.5mm pitch, 5.15x5.15mm EP package4.ZST: Atmel’s code for a VQFN-64, 9x9x0.9mm, 0.5mm pitch, 4.70x4.70mm EP package4.

Variants

- The following acronyms are used to describe a QFN package with a different package height:

- UQFN

- VQFN

- QFN packages come in different pitches (0.40, 0.45, 0.50, 0.65mm).

- QFN packages may or may not have a central exposed pad on the underside.

Dimensions

Common pitches:

- 0.40mm

- 0.45mm

- 0.50mm

- 0.65mm

Note that the max. height for almost any QFN package is 1mm (including stand-off). Some have a smaller height (e.g. the UT/ultra-thin QFN packages).

0.40mm pitch QFN package dimensions (LxWxH):

QFN-UT-20: 3x3x0.6mm (LA: 9mm2) QFN-56: 7x7x1mm (LA: 49mm2) QFN-64: 8x8x1mm (LA: 64mm2) QFN-72: 9x9x1mm (LA: 81mm2) QFN-88: 10x10x1mm (LA: 100mm2) QFN-108: 12x12x1mm (LA: 144mm2)

0.50mm pitch QFN package dimensions (LxWxH):

QFN-16: 3x3x1mm (LA: 9mm2) QFN-20: 3x3x1mm (LA: 9mm2) QFN-24: 4x4x1mm (LA: 16mm2) QFN-32: 5x5x1mm (LA: 25mm2) QFN-36: 6x6x1mm (LA: 36mm2) QFN-48: 7x7x1mm (LA: 49mm2) QFN-56: 8x8x1mm (LA: 64mm2) QFN-64: 9x9x1mm (LA: 81mm2) QFN-68: 10x10x1mm (LA: 100mm2)

0.65mm pitch QFN package dimensions (LxWxH):

QFN-16: 4x4x1mm (LA: 16mm2) QFN-20: 4x4x1mm (LA: 16mm2) QFN-32: 7x7x1mm (LA: 49mm2)

Solderability

Surprisingly easy to solder by hand, as long as the pads extend around to the sides of the IC, and you drill a hole to solder the centre pad from the reverse. QFN packages can also be soldered easily with a infrared rework station or the “frying pan” technique.

Similar To

Solder Mask

TI recommends a non-solder mask defined (NSMD) pad over a solder mask defined (SMD) pad. This is to produce consistent and reliable solder joints. As a rule-of-thumb, you want solder mask openings that are 0.1-0.14mm larger than the pad size. By default, Altium uses NSMD pads.

Some QFN packages have an exposed metal feature on the underside to indicate pin 1. If this is the case, make sure this area is covered with solder mask to prevent shorting to neighbouring traces. This is an unusual feature, and personally I have not used any QFN packages with this present.

The Central Pad And Solder Paste

It is recommended to reduce the amount of solder paste applied to the centre pad (also called the mechanical pad or thermal pad) to prevent the QFN package from floating during reflow. A rule-of-thumb is to have between 50-80% coverage on the center pad (this obviously does not apply to QFN packages with no pad).

It may be necessary to mask or plug vias in the center pad to prevent solder paste being carried through the via and away from the pad during reflow. Small holed vias (such as vias with a hole diameter of 0.3mm or less) do not normally cause a big problem.

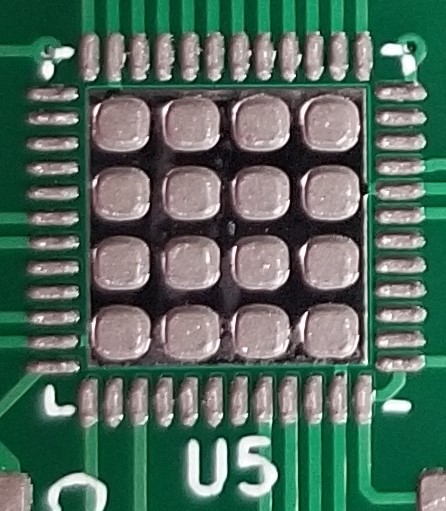

A photo of a 0.5mm pitch QFN footprint on a circuit board with solder paste applied (applied manually with a free-standing stencil, so the alignment is not spot-on, but good enough). You can clearly see the windowing (16 windows in total) on the center pad to reduce the amount of solder paste.

The central pad may not necessarily be electrically connected to anything.

Singulation Methods

There are two singulation methods for QFN packages:

- Punch singulation: This is used on individually-moulded QFN packages.

- Saw singulation: This is used on moulded array QFN packages.

The main difference between these two singulation methods is the cross-sectional profile. Punch singulation gives a tapered cross-section (larger cross-section at the bottom than the top), while sawn singulation gives a completely square cross-section.

Cross-sectional comparison of sawn and punch singulated QFN packages. Image from http://cache.freescale.com/files/analog/doc/app_note/AN1902.pdf.

Punch singulated QFN packages are JEDEC compliant.

Voiding

Volatiles that get trapped underneath the pad during reflow can cause voids to form underneath the component (areas in where the pad is not soldered to the PCB). Another potential cause of voiding is when too much solderpaste is applied to the centre pad, which causes the package to float on the PCB during reflow.

Stresses

Because the QFN package sits directly on the PCB and has no standoff, they are less resilient to mechanical stresses that package with leads such as QFP packages. The amount of PCB board flex must be taken into consideration. Excessive stress can damage a QFN package.

Lead Styles

A QFN package with ’e’ style leads which are fully exposed on the side of the package (this is a good thing).

A QFN package with ‘S’ style leads which are only partially exposed on the side of the package (this is a not a good thing).

Unique Corner Pins

QFN packages exist in where the corner pins have to be of a different shape to all the others for clearance reasons. The only example of this I have ever seen is the package for the IvenSense MPU-9250 IMU. It is a QFN package with 24 pins in a 3x3x1.0mm size with 6 0.40mm pitch pins on each edge. Because of the high pin density, the outer pins on each edge almost touch each other, and so a different pin shape is used. This also means you use a different pad shape for the package footprint.

The footprint for the IvenSense MPU-9250 IMU which uses a QFN package with unique corner pin shapes (notice how they are smaller).

Completely Non-Standard QFN Packages

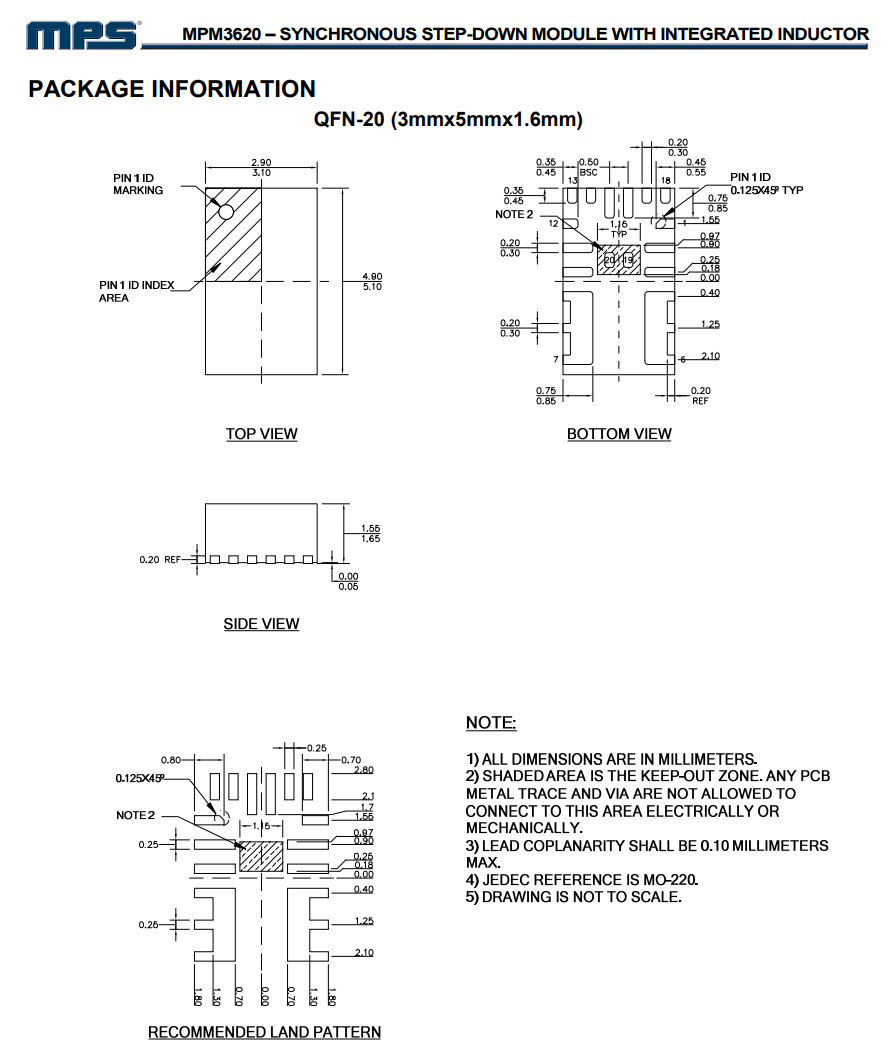

Aside from the unique corner pins that QFN packages can have (as explained above), some QFN packages are completely IC specific and do not follow the “standard” at all. One example is the MPM3620 which comes in a “QFN-20” component package ([^mps-mpm3620-non-standard-qfn-20-component-package]) which has changing pitch, different sized pins, bridged pins and internal pins near the bottom center of the package:

The package dimensions and recommended land pattern for the non-standard QFN-20 package used on the MPS MPM3620 step-down module.

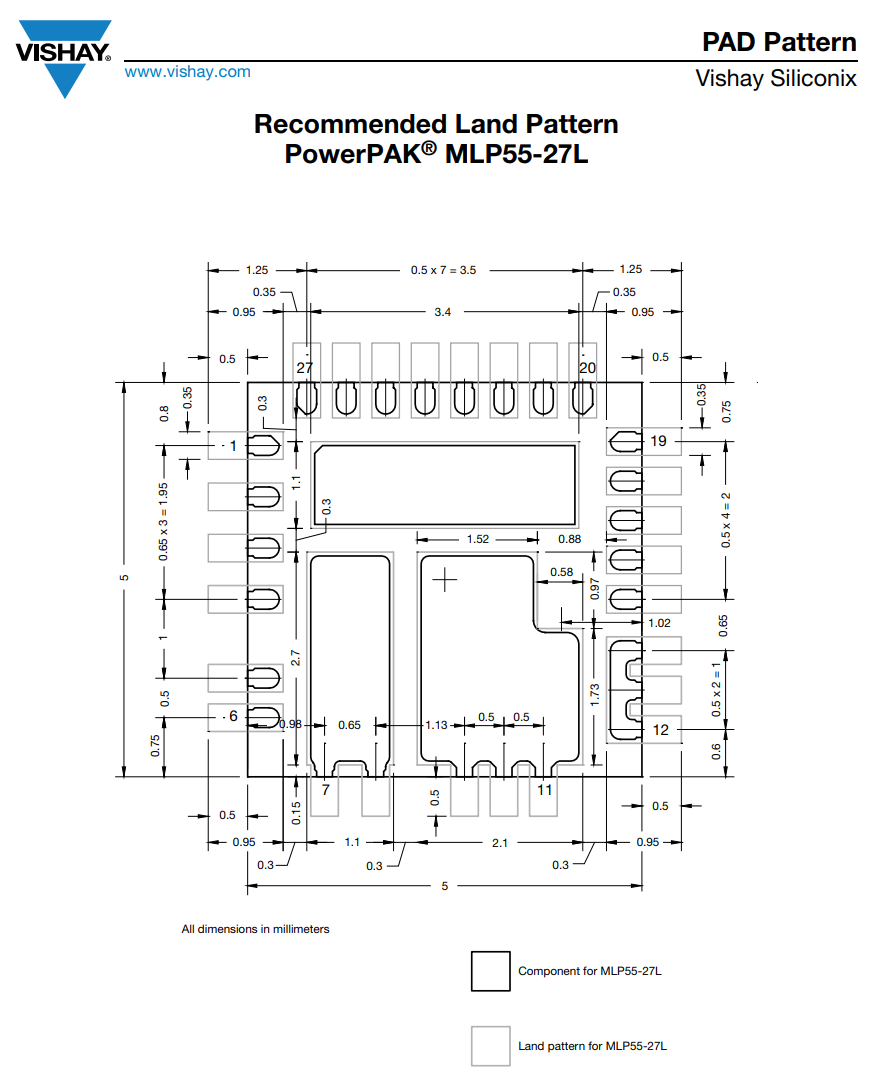

MLP is a common package name used for “non-standard” QFN-like packages, an example is shown below:

Dimensions of the “PowerPAK” MLP55-27L Vishay component package, another “non-standard” and very unique QFN-like package.

Another great example is ST Microelectronic’s PWD13F60 high-voltage full-bridge with integrated gate driver IC. It comes in a VFQFPN 10x13x1.0mm package which contains a variety of pad shapes and sizes, as shown in the below image:

![3D render of the VFQFPN 10x13x1.0mm package used for ST Microelectronic's PWD13F60 IC[^bib-st-pwd13f60-ds].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/st-micro-pwd13f60-vfqfpn-3d-render.png)

3D render of the VFQFPN 10x13x1.0mm package used for ST Microelectronic’s PWD13F60 IC6.

Want to see the recommended footprint for this IC? See below!

![The recommended footprint (land pattern) for the PWD13F60 in the VFQFPN 10x13x1.0mm package[^bib-st-pwd13f60-ds].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/st-micro-pwd13f60-vfqfpn-recommended-footprint.png)

The recommended footprint (land pattern) for the PWD13F60 in the VFQFPN 10x13x1.0mm package6.

Standardization Of Pinout For Logic Functions

JEDEC has a standard on the pinout of QFN packages for logic functions.

JESD75-5 - JEDEC Standard - QFN Pinouts For Logic Functions

Wettable Flanks

Component packages which have wettable flanks have a step-cut lead frame and tin added to the sidewalls of the package. This allows a side fillet of solder to form more reliably, aiding automatic optical inspection (AOI)7 (QFN packages already had pad metallization on the side of the package, but no step-cut nor plating, and side-fillet formation was less reliable).

![Model of the underside of a wettable flank QFN package. Image ©2017, Allegro MicroSystems[^bib-allegro-wettable-flanks].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/wettable-flank-qfn-component-package-underside-allegro.png)

Model of the underside of a wettable flank QFN package. Image ©2017, Allegro MicroSystems8.

![Illustrated cross-section of a wettable flank on a QFN package. Image ©2017, Allegro MicroSystems[^bib-allegro-wettable-flanks].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/wettable-flank-qfn-illustrated-cross-section-allegro.png)

Illustrated cross-section of a wettable flank on a QFN package. Image ©2017, Allegro MicroSystems8.

The QFN package is one of the most common packages for a manufacturer to add wettable flanks to. Wettable flanks was largely driven by the need to AOI in the automotive industry but this package feature is now found to be generally useful in a number of industries.

![Close-up detail drawing highlighting the wettable flanks on the SOT-618(DD) (QFN) component package by NXP. Image ©2018, NXP[^bib-nxp-sot618-13dd].](https://blog.mbedded.ninja/pcb-design/component-packages/qfn-component-package/nxp-sot618-13dd-qfn-wettable-flanks-detail-drawing.png)

Close-up detail drawing highlighting the wettable flanks on the SOT-618(DD) (QFN) component package by NXP. Image ©2018, NXP9.

The tin plating of the flank prevents the traditionally exposed copper (a by-product of the sawing singulation of a single QFN package from a “brick”) from oxidizing8.

Thermal Resistances

LFCSP-16

$$\begin{align} \theta_{JA} = 33.2^{\enspace \circ}C/W \\ \theta_{JB} = 12.4^{\enspace \circ}C/W \\ \theta_{JC} = 2.4^{\enspace \circ}C/W \\ \end{align}$$References

DigiKey. ISL84467IRTZ-T - 4 Circuit IC Switch 2:1 400mOhm (Typ) 16-TQFN (3x3) [Product Page]. Retrieved 2023-08-02, from https://www.digikey.com/en/products/detail/renesas-electronics-america-inc/ISL84467IRTZ-T/1978117. ↩︎

Fairchild Semiconductor (2005, Sep). PCB Land Pattern Design and Surface Mount Guidelines for MLP Packages. Retrieved 2022-03-09, from http://educypedia.karadimov.info/library/AN-5067.pdf. ↩︎

Texas Instruments (2018, May). bq25703A - I2C Multi-Chemistry Battery Buck-Boost Charge Controller With System Power Monitor and Processor Hot Monitor [Datasheet]. Retrieved 2023-08-02, from https://www.ti.com/lit/ds/symlink/bq25703a.pdf. ↩︎

Microchip (2021). SAM D21/DA1 Family Low-Power, 32-bit Cortex-M0+ MCU with Advanced Analog and PWM [Datasheet]. Retrieved 2022-03-02, from https://ww1.microchip.com/downloads/en/DeviceDoc/SAM-D21-DA1-Family-Data-Sheet-DS40001882H.pdf. ↩︎ ↩︎ ↩︎ ↩︎

Linear Technology (now Analog Devices). LT3922-1 - 36V, 2.3A Synchronous Step-Up LED Driver with 25,000:1 PWM Dimming [Datasheet]. Retrieved 2023-08-02, from https://nz.mouser.com/datasheet/2/609/lt3922_1-3123537.pdf. ↩︎

ST Microelectronics (2017, Dec). PWD13F60: High-density power driver - high voltage full bridge with integrated gate driver [Datasheet]. Retrieved 2022-04-19, from https://www.st.com/resource/en/datasheet/pwd13f60.pdf. ↩︎ ↩︎

David Snook (2018, Jan 23). Make automatic optical inspection easy thanks to packages with wettable flanks. Texas Instruments. Retrieved 2021-10-27, from https://e2e.ti.com/blogs_/b/behind_the_wheel/posts/make-automatic-optical-inspection-easy-thanks-to-packages-with-wettable-flanks. ↩︎

Bradley Smith (2017). Wettable Flank Plated PQFN. Allegro Microsystems. Retrieved 2021-10-27, from https://www.allegromicro.com/en/insights-and-innovations/technical-documents/semiconductor-packaging-publications/wettable-flank-plated-pqfn. ↩︎ ↩︎ ↩︎

NXP (2018). SOT618-13(DD) HVQFN40, plastic thermal enhanced very thin quad flat package; no leads, wettable flanks; 40 terminals; 0.5 mm pitch, 6 mm x 6 mm x 0.85 mm body. Retrieved 2021-10-28, from https://www.nxp.com/docs/en/package-information/SOT618-13(DD).pdf. ↩︎

Authors

This work is licensed under a Creative Commons Attribution 4.0 International License .

Related Content:

- LFCSP Component Package

- PCB Layers

- TO-273AA Component Package

- SC-101 Component Package

- SMD-220 Component Package

Tags

- component packages

- PCB design

- QFN

- LFCSP

- MLF

- DO-214AC

- solder paste

- soldermask

- singulation

- voiding

- lead styles

- JEDEC

- package stress